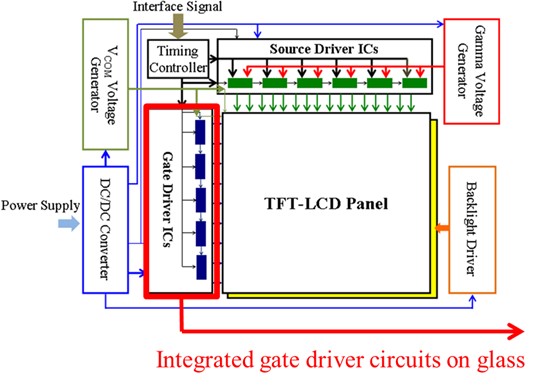

| 一、研究目標 閘極驅動電路(GOA)將驅動電路透過薄膜電晶體(Thin-Film Transistor)技術將電路直接製作於玻璃基板內部如下圖所示,可取代所需驅動IC,並提升整體面板系統穩定性,進而實現低成本、高可靠度顯示器,因此閘極驅動電路已是目前主流顯示技術,而本實驗室亦根據不同顯示器之需求議題,例如:內嵌式觸控面板、低功耗、窄邊框、高解析度…等議題進行設計,並提出相關研究成果如下所示。 |

|

|

|

| 二、研究內容 1. 內嵌式觸控面板 本實驗室於IEEE Transactions on Industrial Electronics提出一雙向閘極驅動電路,主要將重新充電架構及時域分割驅動方法應用於 a-Si:H內嵌式觸控液晶顯示器中,目的在於解決內嵌式觸控之Display-to-touch crosstalk (DTX)現象及觸控回報率不足之問題,同時減緩 a-Si:H 驅動 TFT 因長時間偏壓而造成 VTH飄移之問題,由量測結果顯示所提出電路不僅可以成功實現雙向傳輸功能,同時在經過觸控感測階段後,仍可成功輸出連續波形。 |

||

|

|

|

所提出適用於內嵌式觸控面板之閘極驅動電路架構及系統量測及輸出波形圖 |

||

|

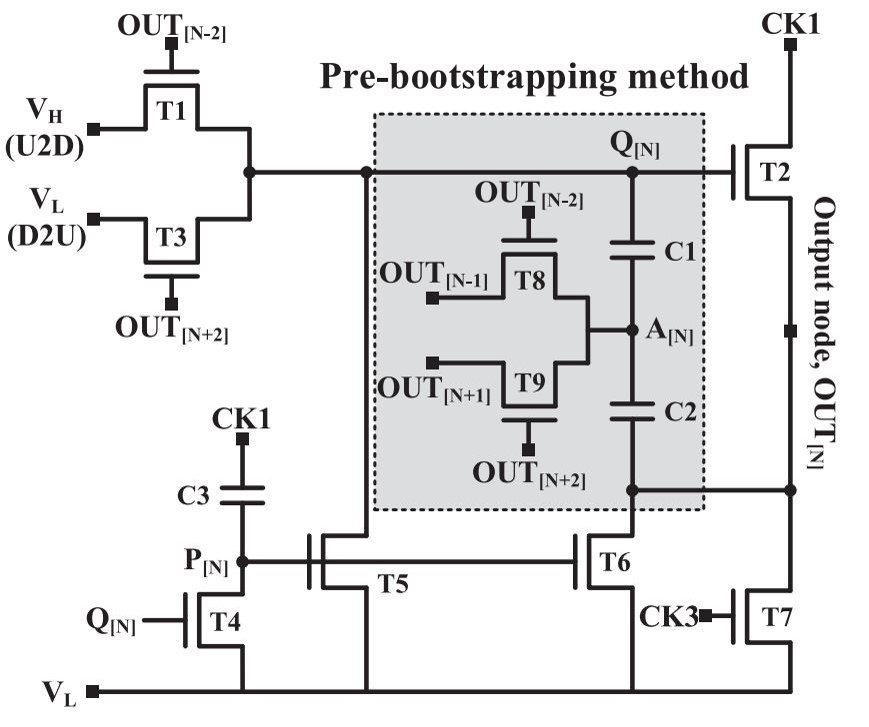

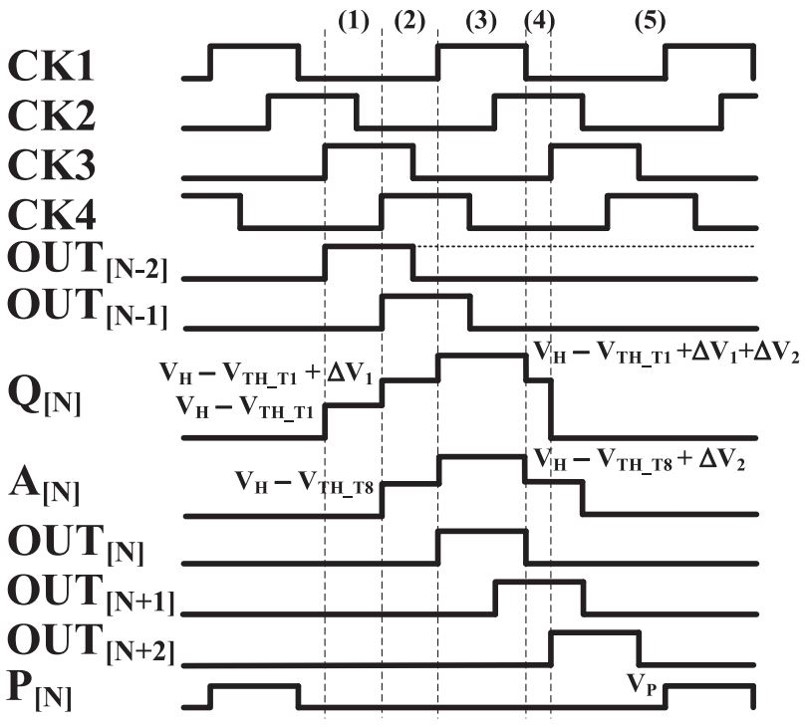

2. 高解析度

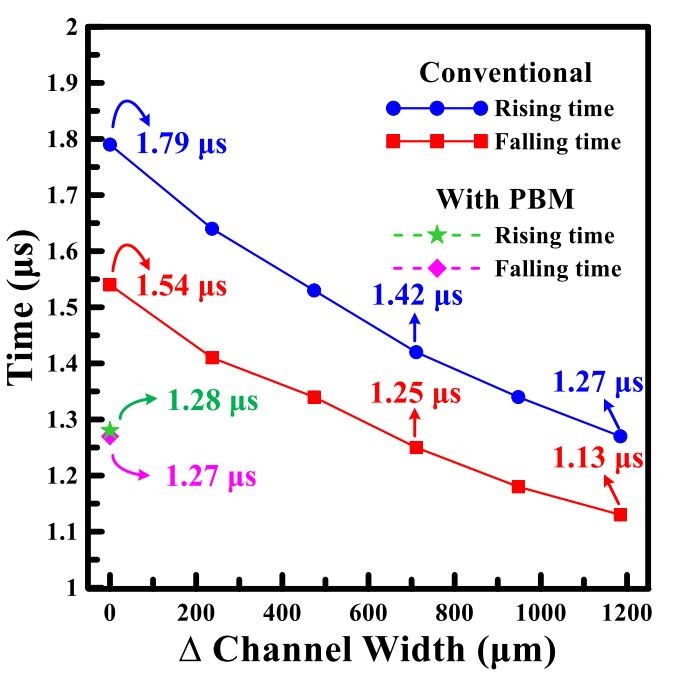

本實驗室於IEEE Transactions on Industrial Electronics提出一採a-Si:H TFT之雙向閘極驅動電路。a-Si:H TFT 因為載子遷移率較低,而在佈局面積有限的情況下TFT通道寬度能調整的幅度有限,在高幀數、高解析度的顯示器下會出現驅動能力不足的問題,故所提出電路透過預抬升方法(Pre-Bootstrapping Method),藉兩次性提高驅動 TFT 閘極電壓來增加a-Si:H TFT 驅動能力。 |

|||

(a) |

(b) |

||

(c) |

(d) |

||

(a) 所提出適用於高階析度之閘極驅動電路、 (b) 驅動時序、 (c) 與傳統架構調整通道寬度後之上升、下降時間比較、 (d) 85 °C下電路可靠度測試 |

|||

|

3. 低功耗

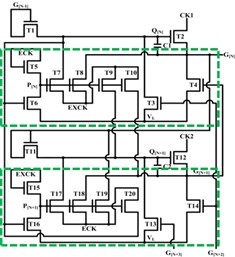

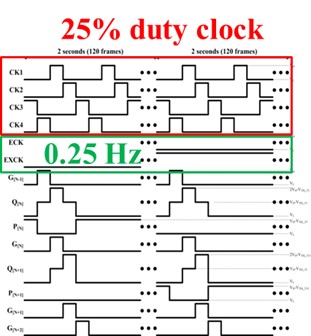

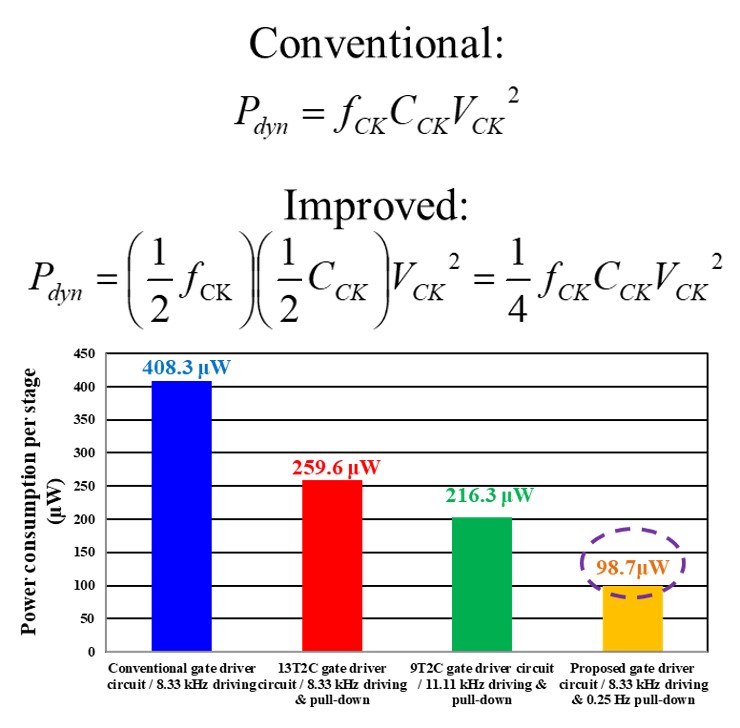

本實驗室所提出之具備低功率消耗且有TFT VTH回復功能之新式閘極驅動電路,透過使用四組驅動時脈(CK1、CK2、CK3和CK4)及兩組額外時脈訊號(ECK和EXCK),利用降低所使用驅動訊號之頻率,來改善電路功率消耗,同時利用低頻率之時脈訊號產生交互反向偏壓(alternative reversed bias stress)來延緩a-Si:H TFT臨界電壓的漂移來達到穩定輸出波形和防止輸出點浮接,而受到時脈訊號轉態時之雜訊影響,確保電路經長時間使用後,輸出仍可保持高穩定性,另外此低頻率之下拉架構被相鄰之兩級閘極驅動電路所共用,可以有效精簡電路之架構。 |

||

|

|

|

所提出低功耗之閘極驅動電路架構、驅動時序圖與其他電路功耗比較圖 |

||

|

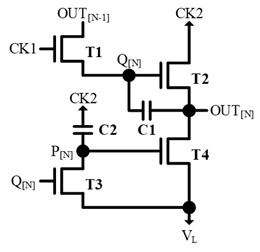

4. 窄邊框

本實驗室提出適用於高解析度及窄邊框顯示器之精簡架構閘極驅動電路,藉由重疊的時脈訊號及輸入薄膜電晶體對驅動電晶體閘極端充放電,並於穩壓階段透過週期性訊號抑制時鐘饋通效應,此外 驅動電晶體被使用來對輸出進行充放電,因此不須額外薄膜電晶體來對輸出進行放電,進而實現精簡架構之電路,此外由模擬結果顯示此電路可成功輸出連續波形,驗證其電路功能,故可適用於高解析度及窄邊框之顯示器應用。 |

||

|

|

|

所提出適用於高階析度和窄邊框顯示器之閘極驅動電路 |

||